̨������ʽ����2nm�Ƴ̣����Ľ���30%��Ԥ��2025������

ʱ�䣺2022-06-18 16:53:42

6 �� 17 ��ѶϢ��̨������ 2022 �꼼�����ֻ��������˹��ڽ��������Ƴ̵���Ϣ��N3 ���ս��� 2022 ������������������ N3E��N3P��N3X �ȣ�N2(2nm)���ս��� 2025 ��������

̨�������������� N3 �� FINFLEX���������������ص�� 3-2 FIN��2-2 FIN �� 2-1 FIN ���ã�

3-2 FIN ����ʱ��Ƶ�κ���ߵĹ���������̱��Ľ���������Ҫ

2-2 FIN Efficient Performance�����ܡ�����Ч�����ܶ�֮�����Խ����

2-1 FIN ������Ч������ġ����¶������ܶ�

̨����� FINFLEX ������ 3nm ϵ�а뵼�弼�յIJ�Ʒ���ܡ�����Ч�����ܶȹ�ģ������оƬ��ְԱ������ͬ�IJ�����ΪͬһоƬ�ϵ�ÿ���ؼ����ܿ�������ѡ�

���� N2 ���棬̨������������һ�����ò���դ������� (GAAFET) �Ľڵ㣬���Ƕ���� FinFET(��ʽ��ЧӦ�����)���µĴ��칤�ս���Ӧ��ȫ�Ĺ��ܺ����Ϸ硣����ͬ�����£�N2 �� N3E ���ʿ� 10~15%;��ͬ�����£��������� 25~30%�����⣬�� N3E ���⣬N2 ����оƬ�ܶ������� 10% ���¡�

N2 ���մ�����������Ҫ�ķ��£�����Ƭ�����(̨�����֮Ϊ GAAFET)�� backside power rail��GAA ����Ƭ����ܵ�ͨ����һ���ĸ�һ�߶���դ��ͻΧ���Ӷ�������¶;���⣬���ǵ�ͨ���ܹ��ӿ������������������������ܣ�Ҳ�ܹ���С������ȵ����߹��ĺͳɱ���Ϊ�˸���Щ����Ƭ����ܹ�Ӧ����Ĺ��ʣ�̨����� N2 ���� backside power rail��̨������Ϊ������ back-end-of-line (BEOL) �п���������ô����ƻ�֮һ��

̨���罫 N2 ���ն�λ�ڸ����ƶ� SoC�������� CPU �� GPU��������ʾ���Σ�������ȼ��������Գ�¯������Ϥ��

�����Ƽ�

-

LOL13.7�汾��ʽ������֮���ǿһ��Ӣ������LOL��Ϊһ�����ŵ������������Ϸ��С����Ҫ֧���ɫ�Ͳ�ͬ��ԩ�ҽ�����ս���в���С�������Ϸ��������LOL13.7�汾��ʽ������֮��ǿ��һ�����Ƶ�����

LOL13.7�汾��ʽ������֮���ǿһ��Ӣ������LOL��Ϊһ�����ŵ������������Ϸ��С����Ҫ֧���ɫ�Ͳ�ͬ��ԩ�ҽ�����ս���в���С�������Ϸ��������LOL13.7�汾��ʽ������֮��ǿ��һ�����Ƶ����� -

���ƶ�֮�ġ�13.7�汾��ʽ���ڿ������������Ϊ���Ѵ����ƶ�֮��13.7�汾��ʽ���ڿͼ����������ϸ�������Ǻö����Ѷ�������һ�����ѣ�������һ�������ƾ������ɲ���

���ƶ�֮�ġ�13.7�汾��ʽ���ڿ������������Ϊ���Ѵ����ƶ�֮��13.7�汾��ʽ���ڿͼ����������ϸ�������Ǻö����Ѷ�������һ�����ѣ�������һ�������ƾ������ɲ��� -

�Զ����Ҵ��ߡ�����־��ɽ��ս�͡���ʽ���� �õ�Ļ��ͷ��Ц��������������־��ɽ��ս�͡���һ��ˮī�����Ҵ��߸����Ϸ������Ϸ�����ܹ�ʹ�������еľ����ɫ��ħ���ǶԴ��ڶԴ��У����ܹ����Ը��Ľ�ɫ��Сʯ������������ʥ��������Ϊ����

�Զ����Ҵ��ߡ�����־��ɽ��ս�͡���ʽ���� �õ�Ļ��ͷ��Ц��������������־��ɽ��ս�͡���һ��ˮī�����Ҵ��߸����Ϸ������Ϸ�����ܹ�ʹ�������еľ����ɫ��ħ���ǶԴ��ڶԴ��У����ܹ����Ը��Ľ�ɫ��Сʯ������������ʥ��������Ϊ���� -

���Ƶ���ð����Ϸ��ħ�����³ǡ���ʽ���ۣ����ѵ�½Steamħ�����³���һ����³�ð����Ϸ��������ManalithStudios��������ϷĿ�µ����Ѿ���Steam�̵���ʽ�����ˣ�����92Ԫ����Ϸ֧�ּ������ģ������С����

���Ƶ���ð����Ϸ��ħ�����³ǡ���ʽ���ۣ����ѵ�½Steamħ�����³���һ����³�ð����Ϸ��������ManalithStudios��������ϷĿ�µ����Ѿ���Steam�̵���ʽ�����ˣ�����92Ԫ����Ϸ֧�ּ������ģ������С���� -

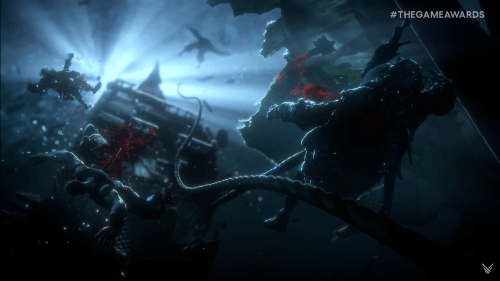

TGA 2023�������˲�Ϣ����ʽ�����������ա����������ڱ��վٰ��TGA223�佱�����ϣ������ա�������������NoRestfortheWicked�������룺���˲��ߣ�����������Ƭ������һ���ֽŽ�ɫ������Ϸ��һ�������

TGA 2023�������˲�Ϣ����ʽ�����������ա����������ڱ��վٰ��TGA223�佱�����ϣ������ա�������������NoRestfortheWicked�������룺���˲��ߣ�����������Ƭ������һ���ֽŽ�ɫ������Ϸ��һ������� -

������ʮ���������������ڱ��¹�������ʱ�����գ���λ��������ڴ��Ѿõ�������Ϸ����ʮ�������ڹ����˱����Ĺ���ʱ�䣬����ʮ�����ٷ����������ڱ��¹�����Ϸ�Ĺ���ʱ��

������ʮ���������������ڱ��¹�������ʱ�����գ���λ��������ڴ��Ѿõ�������Ϸ����ʮ�������ڹ����˱����Ĺ���ʱ�䣬����ʮ�����ٷ����������ڱ��¹�����Ϸ�Ĺ���ʱ�� -

������������ʵ��PV������ԤԼ����ѿ������������ٷ�������������Ϸ��ʽ����5��23�տ������⣬ԤԼ����ѿ�����ͬʱ�ر�ͨѶ������������������Ԥ��ʵ��PV�����ѡ�Ҳ�ѹ���

������������ʵ��PV������ԤԼ����ѿ������������ٷ�������������Ϸ��ʽ����5��23�տ������⣬ԤԼ����ѿ�����ͬʱ�ر�ͨѶ������������������Ԥ��ʵ��PV�����ѡ�Ҳ�ѹ��� -

����Ī���ء�������Ϸ������̫�����������������գ���224��δ����Ϸչ�ϣ�FunPlus��������Skydance��AppleTV������������Ϸ��ĿFoundation:GalacticFrontier

����Ī���ء�������Ϸ������̫�����������������գ���224��δ����Ϸչ�ϣ�FunPlus��������Skydance��AppleTV������������Ϸ��ĿFoundation:GalacticFrontier -

��ʹ���ٻ���ս����������������Ƭ������4��3��������ߣ���ʹ���ٻ����ٷ����չ����ˡ�ʹ���ٻ���ս������������������Ƭ����ͼ��������������������������4��3����ʽ����������ͬ���������ΰ�

��ʹ���ٻ���ս����������������Ƭ������4��3��������ߣ���ʹ���ٻ����ٷ����չ����ˡ�ʹ���ٻ���ս������������������Ƭ����ͼ��������������������������4��3����ʽ����������ͬ���������ΰ� -

�ֲ�������Ϸ����ʬģ���������������� ������������ҽ��ģ��/�ֲ���Ϸ����ʬģ�����������������ڣ�����224��5��1�յ�½Steamƽ̨����Ϸ֧�ּ�������

�ֲ�������Ϸ����ʬģ���������������� ������������ҽ��ģ��/�ֲ���Ϸ����ʬģ�����������������ڣ�����224��5��1�յ�½Steamƽ̨����Ϸ֧�ּ������� -

̨������ʽ����2nm�Ƴ̣����Ľ���30%��Ԥ��2025������6 �� 17 ��ѶϢ��̨������ 2022 �꼼�����ֻ��������˹��ڽ��������Ƴ̵���Ϣ��N3 ���ս��� 2022 ������������������ N3E��N3P��N3X �ȣ�N2(2nm)���ս��� 2025 ��������

̨������ʽ����2nm�Ƴ̣����Ľ���30%��Ԥ��2025������6 �� 17 ��ѶϢ��̨������ 2022 �꼼�����ֻ��������˹��ڽ��������Ƴ̵���Ϣ��N3 ���ս��� 2022 ������������������ N3E��N3P��N3X �ȣ�N2(2nm)���ս��� 2025 �������� -

msiafterburnerû���Կ����Ľ������MSIAfterburner��һ��ǿ����Կ����ƺͳ�Ƶ���ߣ�������ʱ�����ѿ��ܻ�����һ�����⣬����ʹ��MSIAfterburnerʱ������ʾ�Կ�����

-

����8gen2��8+�ĸ��� ���IJ���������ܶԱ�����˭��ǿ����8gen2��8+�ĸ��� ���IJ���������ܶԱ�����˭��ǿ

-

����778g������985�ĸ��� ��������˭���ĸ���ǿ����778g������985�ĸ��� ��������˭���ĸ���ǿ

����778g������985�ĸ��� ��������˭���ĸ���ǿ����778g������985�ĸ��� ��������˭���ĸ���ǿ -

AMD RX 7000ϵ�н���11��3�շ��� �Կ������ع�AMD RX 7000ϵ�н���11��3�շ��� �Կ������ع�

AMD RX 7000ϵ�н���11��3�շ��� �Կ������ع�AMD RX 7000ϵ�н���11��3�շ��� �Կ������ع� -

DLSS 3��RTX 40�Կ�����1/4���ģ�Ƶ�����¶ȱ��ֳ�ɫNVIDIA RTX���Կ��ķ�ͷ������Ӣΰ���������һ�ѻ���GeForce RTX 4090�Կ�������һ�¡�������� 2077����Ϸ���ܣ���2.85 GHz��Ƶ���£����Կ��Կ��Խ��¶Ȳ����� 50�棬�����������ѧϰ������������(DLSS 3)�ɽ�����GPU���ʸߴ� 25% ��

DLSS 3��RTX 40�Կ�����1/4���ģ�Ƶ�����¶ȱ��ֳ�ɫNVIDIA RTX���Կ��ķ�ͷ������Ӣΰ���������һ�ѻ���GeForce RTX 4090�Կ�������һ�¡�������� 2077����Ϸ���ܣ���2.85 GHz��Ƶ���£����Կ��Կ��Խ��¶Ȳ����� 50�棬�����������ѧϰ������������(DLSS 3)�ɽ�����GPU���ʸߴ� 25% �� -

������־�������ǻ���ô���� ������־�������ǻ۹���������־�������ǻ�Ӧ����β����أ�����Dz�������С������ɻ�ĵط��ˣ��ǻ���ֵ����Ϸ�е��ô��dz����ǽ��������Ի��һ��ר���ɾ��Լ��ƺţ�����С�����Ҵ�����

������־�������ǻ���ô���� ������־�������ǻ۹���������־�������ǻ�Ӧ����β����أ�����Dz�������С������ɻ�ĵط��ˣ��ǻ���ֵ����Ϸ�е��ô��dz����ǽ��������Ի��һ��ר���ɾ��Լ��ƺţ�����С�����Ҵ����� -

��������ſն�ѹ��ֵ��ô�����ھ�������Ϸ�У��Ϳն�ѹ��ֵ�ܸ�����Ҹ������ơ���ҿ�ͨ�������ض�����Ч���Լ��ٿն���ѹ��ֵ���������������������������侲���������ȴ��������ն���������ʱ

��������ſն�ѹ��ֵ��ô�����ھ�������Ϸ�У��Ϳն�ѹ��ֵ�ܸ�����Ҹ������ơ���ҿ�ͨ�������ض�����Ч���Լ��ٿն���ѹ��ֵ���������������������������侲���������ȴ��������ն���������ʱ -

��������ſն�ѹ��ֵ���ͷ���Ϊ�������Ϸ���飬���������ſն���Ѱ�ҿ��Խ���ѹ��ֵ����Ʒ���ܡ�ͨ��ѧϰʹ����Щ����������Ը����̽����ſն���������Ч��Ӧ����ս

��������ſն�ѹ��ֵ���ͷ���Ϊ�������Ϸ���飬���������ſն���Ѱ�ҿ��Խ���ѹ��ֵ����Ʒ���ܡ�ͨ��ѧϰʹ����Щ����������Ը����̽����ſն���������Ч��Ӧ����ս -

��������ſն���ô����ѹ��ֵ_��������ſն�����ѹ��ֵ����������������ſն�����ѹ��ֵ�������ܣ����������κܶ��淨����ͦ��ģ�������Ϸ����ſն�ѹ��ֵ��ν����أ�������һ��Dz��˽�ģ�С����������ſն�����ѹ��ֵ����������һ����������ص���Ϣ��

��������ſն���ô����ѹ��ֵ_��������ſն�����ѹ��ֵ����������������ſն�����ѹ��ֵ�������ܣ����������κܶ��淨����ͦ��ģ�������Ϸ����ſն�ѹ��ֵ��ν����أ�������һ��Dz��˽�ģ�С����������ſն�����ѹ��ֵ����������һ����������ص���Ϣ�� -

�����С��ٷ�������ӵ���Ϸģʽ�����������ӳ�PS5��ռ������Ϸ�����С��Ѿ�����������������棬һЩ��ҿ��ܻ����������ӳٵ����⣬���Դˣ����йٷ������˽���

�����С��ٷ�������ӵ���Ϸģʽ�����������ӳ�PS5��ռ������Ϸ�����С��Ѿ�����������������棬һЩ��ҿ��ܻ����������ӳٵ����⣬���Դˣ����йٷ������˽��� -

iPhone16plus����Ǯ-iPhone16plusԤ���ۼ�ͼ�Ľ���iPhone16plus���в�Ʒѡ����Ȼ�����ʲ��ϣ���ȩ����������������ܾ�ӫ��������ĸӤ��Ʒ��֤����A����������С�����iPhone16plusԤ���ۼ���Ϣ���뻻�ֻ����û���ǧ��Ҫ����Ŷ��iPhone16plus����Ǯ�����7000Ԫ���ң����Dz�ͬ�ڴ�۸�ͬ�������Թٷ�Ϊ��iPhone 16 Pro ��ʾ���� 6.1 Ӣ������Ϊ 6.3 Ӣ�磬iPhone 16 Pro Max

iPhone16plus����Ǯ-iPhone16plusԤ���ۼ�ͼ�Ľ���iPhone16plus���в�Ʒѡ����Ȼ�����ʲ��ϣ���ȩ����������������ܾ�ӫ��������ĸӤ��Ʒ��֤����A����������С�����iPhone16plusԤ���ۼ���Ϣ���뻻�ֻ����û���ǧ��Ҫ����Ŷ��iPhone16plus����Ǯ�����7000Ԫ���ң����Dz�ͬ�ڴ�۸�ͬ�������Թٷ�Ϊ��iPhone 16 Pro ��ʾ���� 6.1 Ӣ������Ϊ 6.3 Ӣ�磬iPhone 16 Pro Max -

����֮��4��������Ԥ�� Ԥ��2025����ʽ����������֮����ʽ��������һ��Ϣ��Դ���������������Ԥ��Ƭ����Ϸ�������ϲ����ϵ�б��ܹ�ע������֮��4��������Ԥ��Ԥ��225����ʽ��������֮��4�ڲ���ǰ���������µ���

����֮��4��������Ԥ�� Ԥ��2025����ʽ����������֮����ʽ��������һ��Ϣ��Դ���������������Ԥ��Ƭ����Ϸ�������ϲ����ϵ�б��ܹ�ע������֮��4��������Ԥ��Ԥ��225����ʽ��������֮��4�ڲ���ǰ���������µ��� -

С���ֻ�9��֧�־��������Ϸ������ȫ���� Ԥ��7��19�շ�������С��������̬������С���ֻ����Һ�������ȫ����JUSTDANCE����ΪNintendoSwitch��Ҵ���ȫ������

С���ֻ�9��֧�־��������Ϸ������ȫ���� Ԥ��7��19�շ�������С��������̬������С���ֻ����Һ�������ȫ����JUSTDANCE����ΪNintendoSwitch��Ҵ���ȫ������ -

�������ʲôʱ����-������շ���ʱ��Ԥ��������գ����ص�ʷʫʱ����������ʵ��֯�������У�һ����Ϊ������յ���Ϸ��������ʽ���ۣ�����ҳ����ڳ�����˼��ð�վ����������

�������ʲôʱ����-������շ���ʱ��Ԥ��������գ����ص�ʷʫʱ����������ʵ��֯�������У�һ����Ϊ������յ���Ϸ��������ʽ���ۣ�����ҳ����ڳ�����˼��ð�վ���������� -

������ҫ2024��һ������ЩƤ�������� ��һԤ�Ʒ���Ƥ��һ��������һ���ڵ��ٽ���������ҫΪ�˻�����ң�������һ�ڼ����һϵ�л���ⲻ��������Ȥ�Ľ��ջ���������������Ӣ��Ƥ����������ʱ����

������ҫ2024��һ������ЩƤ�������� ��һԤ�Ʒ���Ƥ��һ��������һ���ڵ��ٽ���������ҫΪ�˻�����ң�������һ�ڼ����һϵ�л���ⲻ��������Ȥ�Ľ��ջ���������������Ӣ��Ƥ����������ʱ���� -

������³Ƥ����ô���� ������³Ƥ��������������������³��һ��������ʤ�Ľ�ɫ��������Ϸ����Ϸ�еIJ�������ʮ�ַḻ�����а���Ƥ������Ϸ��Ƥ����Դ��Ϊϡȱ�һ�ȡ����

-

��������³��ţ��������������������³ţ���������?�����������³����ұ�Ҫ�õ�ţ�̣���������̫��������³ţ�������������֪��ţ����β��ܻ�ȡ�ıȽ϶࣬������С������Ѵ���������³ţ������

��������³��ţ��������������������³ţ���������?�����������³����ұ�Ҫ�õ�ţ�̣���������̫��������³ţ�������������֪��ţ����β��ܻ�ȡ�ıȽ϶࣬������С������Ѵ���������³ţ������ -

δ��Ҫȡ��iPhone��ƻ��XR�豸����2023��Q1������8K�ֱ������ṩ��������Ϣ��ƻ����XR(����ʵ��)�豸��ΪN301��������2023���һ�������������࣬ƻ���������ṩ���ð뵼�����Ҹ�ʽƴװ������һ�������ư�

δ��Ҫȡ��iPhone��ƻ��XR�豸����2023��Q1������8K�ֱ������ṩ��������Ϣ��ƻ����XR(����ʵ��)�豸��ΪN301��������2023���һ�������������࣬ƻ���������ṩ���ð뵼�����Ҹ�ʽƴװ������һ�������ư� -

��������������8��V-NAND���� �����Ľ��洢�ܶ��봫�������������������� 8 �� V-NAND ���棬�̺������Ƴ��� PCIe 5.0 SSD ���ڵIJ�Ʒ��������Ϊ�û�����˶��Ĵ洢������������������������ V-NAND ������ 236 �㣬ͬ�ȴ洢����������Ҳ�ɱ�ø��ӽ��ա���Ϊ�ο���ȥ�귢���ĵ� 7 �� V-NAND �����ṩ 176 �㡢�����ߴ� 2.0 GT/s �Ĵ������ʡ�

��������������8��V-NAND���� �����Ľ��洢�ܶ��봫�������������������� 8 �� V-NAND ���棬�̺������Ƴ��� PCIe 5.0 SSD ���ڵIJ�Ʒ��������Ϊ�û�����˶��Ĵ洢������������������������ V-NAND ������ 236 �㣬ͬ�ȴ洢����������Ҳ�ɱ�ø��ӽ��ա���Ϊ�ο���ȥ�귢���ĵ� 7 �� V-NAND �����ṩ 176 �㡢�����ߴ� 2.0 GT/s �Ĵ������ʡ�

���¸���

-

ԭ��10.31���¶һ���2024����

ԭ��10.31���¶һ���2024����

-

LOL�ڶ�������ͷ����û��theshy����

LOL�ڶ�������ͷ����û��theshy����

-

�²¡���ʿ�y�����������ֺ���������ͬ�ࣿ

�²¡���ʿ�y�����������ֺ���������ͬ�ࣿ

-

wowħ������11.0���ؾ���������������

wowħ������11.0���ؾ���������������

-

wowħ������20���������̳����ͼ�Ĺ���

wowħ������20���������̳����ͼ�Ĺ���

-

�����������10.31�һ���2024����

�����������10.31�һ���2024����

-

�λ����ζػ�ҹ̷�Ͻ���ƻ�ȡ����

�λ����ζػ�ҹ̷�Ͻ���ƻ�ȡ����

-

�λ�����һ����boss���ɹ���

�λ�����һ����boss���ɹ���

-

��������10.31���¼�����2024����

��������10.31���¼�����2024����

-

�ҵ�����10.31���¶һ���2024����

�ҵ�����10.31���¶һ���2024����

-

ħ����������ʱ���ٵ�������������

ħ����������ʱ���ٵ�������������